| TI Application Note Nixie Clock | |

|

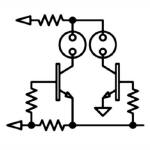

Schematic TES Redesign This application note from the '70s shows how to build a nixie clock from hard logic blocks (Gates, counters etc). It uses a transformer for mains isolation with a low voltage winding to run the logic and a high volage winding to power the tube anodes. Line frequency is pulled off the AC and fed into a on-shot that prevent slow rise and fall timing of the line waveform from multi-pulsing the counting circuits: after being triggered, the one shot ignores all transitions to its input for 1-1/2 half cycles. The notes to the left are corrections to the original circuit as well as enhancements. |